高速MOS模擬集成電路中的靜電保護電路設(shè)計

靜電放電(ESD)是集成電路(IC)制造和應(yīng)用過程中常見且具有破壞性的現(xiàn)象,尤其對高速MOS模擬集成電路而言,ESD保護電路的設(shè)計至關(guān)重要。在高速模擬電路中,MOS器件對電壓和電流的瞬態(tài)變化極為敏感,ESD事件可能導致器件永久性損壞、性能退化或功能失效。因此,設(shè)計有效的靜電保護電路不僅需要滿足ESD防護標準(如人體模型HBM、機器模型MM和充電器件模型CDM),還需兼顧高速模擬電路對信號完整性、帶寬和噪聲的要求。

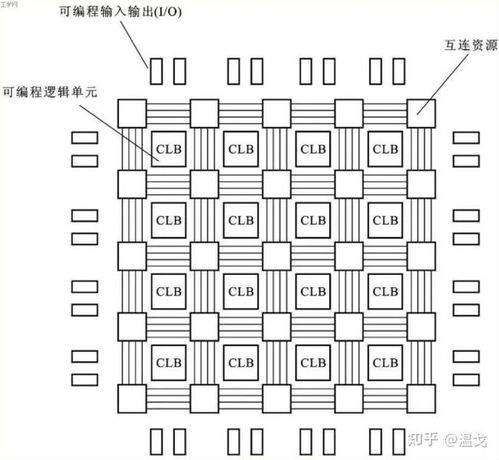

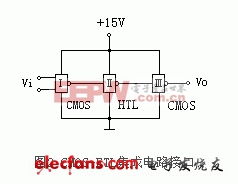

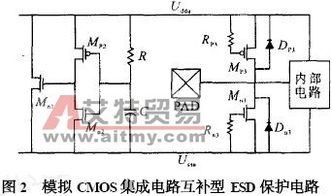

靜電保護電路的基本原理是在集成電路的輸入/輸出(I/O)引腳和電源引腳處引入保護結(jié)構(gòu),以在ESD事件發(fā)生時提供低阻抗路徑,將靜電能量安全泄放到地或電源線,從而保護內(nèi)部核心電路。常見的保護器件包括二極管、MOS晶體管、硅控整流器(SCR)和電阻-電容網(wǎng)絡(luò)。在高速MOS模擬IC中,設(shè)計需特別注意以下幾個方面:保護電路的寄生電容和電阻應(yīng)最小化,以避免對高頻信號的衰減和相位失真;保護結(jié)構(gòu)的觸發(fā)電壓和維持電壓需精確控制,確保在正常操作下不激活,而在ESD事件下快速響應(yīng);布局優(yōu)化至關(guān)重要,例如采用分布式保護策略,將保護元件靠近I/O焊盤,以減少ESD路徑中的電感效應(yīng)。

實際設(shè)計中,工程師常采用多級保護方案:第一級為初級保護,使用大尺寸二極管或SCR以吸收大部分ESD能量;第二級為次級保護,針對核心電路中的敏感MOS器件,設(shè)計更精細的保護結(jié)構(gòu)。例如,在高速運算放大器或數(shù)據(jù)轉(zhuǎn)換器中,可在差分輸入對管附近集成柵極接地NMOS(GGNMOS)或電阻-電容耦合的保護電路,以平衡ESD魯棒性和電路性能。仿真工具如SPICE和TCAD在設(shè)計中不可或缺,通過模擬ESD脈沖下的電流-電壓特性,優(yōu)化器件尺寸和拓撲。

高速MOS模擬集成電路的靜電保護電路設(shè)計是一個多學科交叉的挑戰(zhàn),需要深入理解器件物理、電路理論和工藝限制。隨著工藝節(jié)點向納米尺度演進,ESD防護與高速性能的權(quán)衡將更加尖銳,未來趨勢可能包括新材料(如碳納米管)的應(yīng)用和智能自適應(yīng)保護電路的開發(fā),以提升集成電路的可靠性和壽命。

如若轉(zhuǎn)載,請注明出處:http://m.ybxllbj.cn/product/39.html

更新時間:2026-01-09 06:13:09